Технология упаковки CoWoS

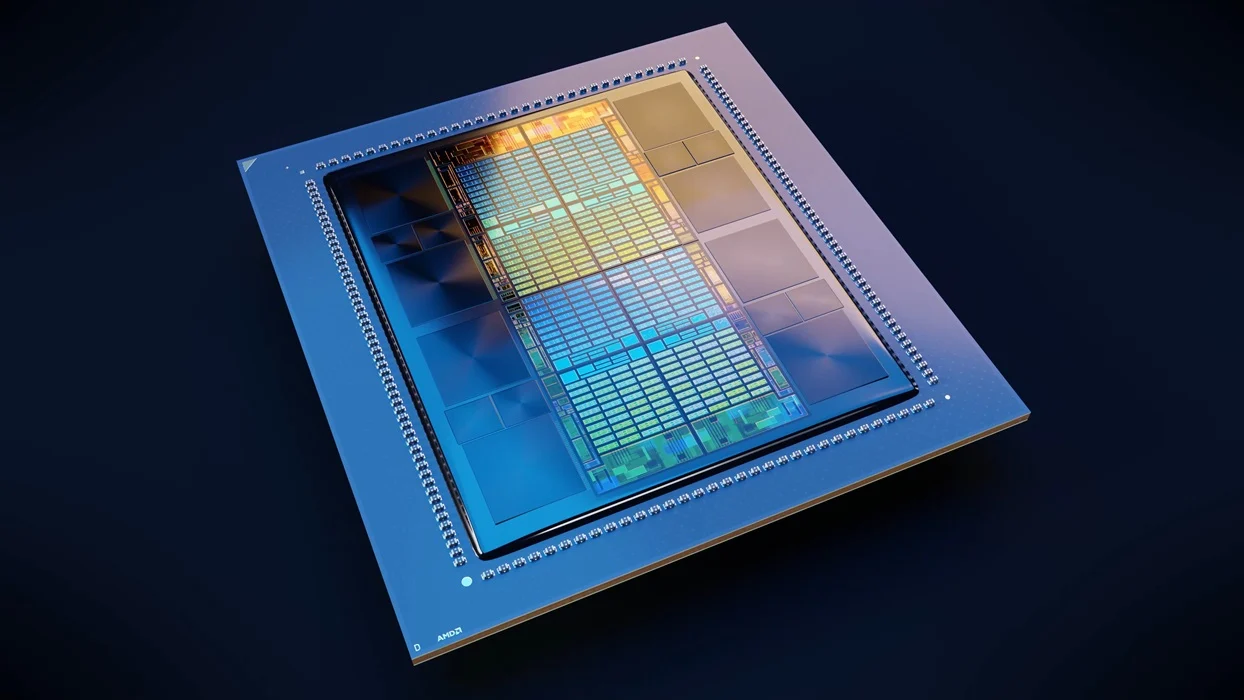

Индустрия высокопроизводительных вычислений и искусственного интеллекта стоит на пороге новой эры благодаря инновационной технологии упаковки "чип на подложке" (CoWoS). Эта передовая разработка открывает беспрецедентные возможности для создания мощных и эффективных вычислительных систем.

Преимущества технологии CoWoS

CoWoS предлагает ряд ключевых преимуществ:

- Увеличенный размер упаковки

- Большее количество соединений ввода-вывода

- Возможность 2,5D- и 3D-интеграции компонентов

- Гетерогенная интеграция логических SoC и памяти HBM

Эта технология стала ответом на растущие потребности в памяти современных центров обработки данных, позволяя эффективно использовать память с высокой пропускной способностью (HBM) для увеличения объема и скорости работы с данными.

Архитектурные инновации

CoWoS представляет собой революционный подход к упаковке чипов, сочетая в себе:

- Горизонтальную укладку 2,5D

- Вертикальную укладку 3D

Такая архитектура позволяет создавать многослойные чиплеты, объединяющие различные модули процессоров и памяти в единую систему. Использование сквозных кремниевых каналов (TSVs) и микровыступов обеспечивает:

- Сокращение длины межсоединений

- Снижение энергопотребления

- Улучшение целостности сигнала

Практическое применение

CoWoS особенно эффективна при интеграции передовых процессоров (GPU, ускорители ИИ) с модулями памяти HBM. Это критически важно для приложений искусственного интеллекта, требующих огромной вычислительной мощности и быстрого доступа к данным.

Размещая элементы обработки и памяти в непосредственной близости друг от друга, CoWoS:

- Минимизирует задержки

- Максимизирует пропускную способность

- Обеспечивает значительный прирост производительности в задачах с интенсивным использованием памяти

Технология CoWoS знаменует собой новый этап в развитии полупроводниковой индустрии, открывая путь к созданию более мощных, эффективных и компактных вычислительных систем будущего.

Ключевые преимущества упаковки CoWoS

Технология CoWoS предлагает ряд существенных преимуществ:

- Масштабирование и более высокий уровень интеграции: CoWoS позволяет преодолеть ограничения закона Мура, удовлетворяя потребности высокопроизводительных вычислений, искусственного интеллекта и GPU-приложений. Технология уменьшает межсоединения между логическими SoC и HBM, что значительно повышает производительность системы.

- Улучшенное терморегулирование: Использование кремниевых и органических интерпозеров в CoWoS существенно расширяет возможности терморегулирования стоечных интегральных схем. Это напрямую повышает общую надежность и долговечность системы, а также минимизирует риски теплового дросселирования.

- Улучшенная целостность питания: CoWoS применяет RDL для сетей питания/земли в интерпозере и использует конденсаторы с глубокой траншеей (DTC). Эти технологии обеспечивают высокую целостность питания для высокоскоростных приложений и приложений с интенсивным использованием памяти.

- Уменьшение размеров и стоимости: Технология CoWoS позволяет монтировать несколько логических SoC и HBM на одном интерпозере и подложке. В отличие от традиционных методов упаковки, где компоненты монтировались на печатную плату, CoWoS значительно уменьшает общие размеры упаковки. Это приводит к снижению материальных затрат и производственных накладных расходов, делая технологию более экономичной.

Технология CoWoS знаменует собой новый этап в развитии полупроводниковой индустрии, открывая путь к созданию более мощных, эффективных и компактных вычислительных систем будущего.

Динамика рынка технологий CoWoS

Драйверы спроса

Бурное развитие таких технологий, как искусственный интеллект, облачные вычисления, аналитика больших данных и мобильные вычисления, привело к росту спроса на вычислительную мощность. Высокая потребность современного общества в вычислительной мощности стимулирует рост числа чипов с искусственным интеллектом, что обуславливает потребность в передовых упаковочных решениях, таких как CoWoS.

Данные TrendForce свидетельствуют о значительном росте поставок AI-серверов. Ожидается, что в 2023 году они достигнут почти 1,2 млн единиц, а прогнозируемый CAGR составит 22% с 2022 по 2026 год. Спрос на чипы ИИ, особенно на графические процессоры с более высокими характеристиками HBM, привел к ограничению мощностей для упаковки CoWoS компании TSMC, основным заказчиком которой является NVIDIA.

Динамика спроса и предложения

Упаковочные мощности TSMC CoWoS стали узким местом для выпуска чипов ИИ из-за нехватки поставок, особенно в сегменте интерпозеров. TSMC планирует удвоить мощности CoWoS и инвестировать в передовые упаковочные фабрики, чтобы устранить дисбаланс спроса и предложения к концу 2024 года.

Другие тайваньские компании, включая UMC, ASE Technology Holding и Powertek Technology, также выходят на рынок передовой упаковки CoWoS. Они наращивают мощности и предлагают альтернативные решения, что должно способствовать удовлетворению растущего спроса на эту технологию.

Разновидности технологии CoWoS

В настоящее время используются три класса технологий CoWoS:

CoWoS-S

В этой технологии используется монолитный кремниевый интерпозер вместе со сквозными кремниевыми каналами (TSV) для прямой передачи высокоскоростных электрических сигналов между матрицей и подложкой. Однако монолитный кремниевый интерпозер может сталкиваться с проблемами выхода продукции.

CoWoS-R

Эта технология заменяет кремниевый интерпозер CoWoS-S органическим интерпозером. Органический интерпозер имеет мелкощелевые RDL для обеспечения высокоскоростного соединения между HBM и матрицей или даже между матрицей и подложкой. В отличие от CoWoS-S, CoWoS-R обеспечивает более высокую надежность и выход годных изделий. Органический интерпозер, будучи по своей природе гибким, действует как буфер напряжения и снижает проблемы надежности, возникающие из-за несоответствия коэффициентов теплового расширения подложки и интерпозера.

CoWoS-L

В этом варианте используется локальное кремниевое межсоединение (LSI) вместе с RDL-интерпозером, образуя восстановленный интерпозер (RI). В дополнение к RDL-интерпозеру сохраняется привлекательная особенность CoWoS-S в виде сквозных кремниевых каналов (TSVs). Это также снижает проблемы с выходом продукции, возникающие из-за использования больших кремниевых промежуточных элементов в CoWoS-S. В некоторых реализациях для минимизации вносимых потерь вместо TSV могут использоваться сквозные изоляционные проходы (TIVs).

Технология CoWoS продолжает развиваться, предлагая различные варианты для удовлетворения специфических потребностей производителей полупроводников и конечных пользователей. Каждая разновидность CoWoS имеет свои преимущества и особенности применения, что позволяет выбирать наиболее подходящее решение для конкретных задач и условий производства.

Компоненты пакета CoWoS

В этом разделе мы рассмотрим составные части пакета CoWoS-L и этапы его изготовления.

CoWoS-L представляет собой сборку "чип-последний", что означает, что сначала изготавливается интерпозер, а затем на него укладываются полупроводниковые матрицы. Интерпозер является одним из ключевых компонентов в технологии CoWoS. На него устанавливаются несколько полупроводниковых матриц, таких как SoC, HBM и другие, обеспечивая эффективное соединение и связь между чипами.

После изготовления интерпозера следующим шагом является создание сквозных изолированных отверстий (TIVs) в полупроводниковых матрицах. Затем на подложку устанавливаются заведомо исправные матрицы (KGD). Зазоры между матрицей и TIV заполняются формовочным компаундом, после чего применяется процесс химико-механической планаризации (CMP) для получения планарной поверхности.

На следующем этапе изготавливаются два слоя перераспределения (RDL). Первый слой RDL создается на лицевой стороне интерпозера для соединения пластины и подложки через μ-переходы. Второй слой RDL формируется на задней стороне интерпозера для соединения интерпозера и подложки с помощью C4-выступов.

Важным компонентом технологии CoWoS-L являются конденсаторы глубокой траншеи (DTC). Эти конденсаторы обеспечивают высокую плотность емкости, что значительно улучшает электрические характеристики системы. DTC выступают в качестве резервуаров для заряда и удовлетворяют мгновенную потребность в токе при работе высокоскоростных вычислительных приложений.

Использование этих компонентов и технологических процессов в CoWoS-L позволяет создавать высокоэффективные упаковочные решения, отвечающие требованиям современных высокопроизводительных вычислительных систем и приложений искусственного интеллекта. CoWoS-L обеспечивает оптимальную интеграцию различных чипов, высокую скорость межсоединений и эффективное управление питанием, что делает эту технологию ключевым элементом в развитии передовых полупроводниковых устройств.

Проблемы и ограничения

Несмотря на многочисленные преимущества, технология CoWoS сталкивается с рядом проблем и ограничений, которые необходимо учитывать при ее применении.

- Сложность производства и стоимость: Технология CoWoS, представляющая собой 2,5D/3D интеграцию, отличается значительной сложностью производства по сравнению со своими предшественниками. Эта сложность напрямую приводит к увеличению стоимости чипов, использующих данную технологию упаковки. Это считается одной из основных причин роста стоимости чипов для высокопроизводительных вычислений и искусственного интеллекта в последнее время. Кроме того, стоимость тестирования CoWoS также вносит свой вклад в общее удорожание продукции.

- Интеграция и проблемы с производительностью: Тестирование 2,5D- и 3D-интегральных схем представляет собой сложную задачу. Каждую пластину необходимо тестировать отдельно перед установкой на интерпозер, а затем еще раз после монтажа. Также требуется проверка сквозных кремниевых каналов (TSV). Особую проблему представляют большие кремниевые интерпозеры, которые чувствительны к производственным дефектам, что может привести к потере производительности.

- Тепловые проблемы: Корпуса CoWoS страдают от тепловых проблем из-за разницы в коэффициенте теплового расширения (CTE) между интерпозером и подложкой. Хотя использование органических интерпозеров в некоторой степени ограничивает эти проблемы, все еще существуют вызовы. Срок службы паяного соединения может быть значительно увеличен за счет использования материала подложки, который компенсирует тепловое несоответствие между кремниевой матрицей и подложкой. На лицевой стороне целостность слоя перераспределения (RDL), особенно под двумя кремниевыми матрицами, подвержена стрессу. Использование подложки μ-bump выступает в качестве буфера напряжения между кремниевыми матрицами и RDL, помогая смягчить эти проблемы.

- Электрические проблемы: Пакеты CoWoS сталкиваются с электрическими проблемами в виде нарушения целостности сигнала и питания. Проблемы целостности сигнала возникают в межсоединениях между логическими пластинами и подложками, а также между логической подложкой и HBM. При увеличении скорости передачи данных межсоединения испытывают ухудшение передачи сигнала из-за паразитной емкости и индуктивности TSV. Для решения этой проблемы ведутся работы по оптимизации TSV с целью минимизации емкости и индуктивности. Что касается целостности питания, пакеты CoWoS обычно используются в высокопроизводительных приложениях с высокой скоростью переключения данных и низким рабочим напряжением, что делает их восприимчивыми к проблемам в этой области.

Несмотря на эти вызовы, технология CoWoS продолжает развиваться и совершенствоваться. Производители и исследователи активно работают над решением этих проблем, что позволяет расширять возможности применения CoWoS в различных областях высокопроизводительных вычислений и искусственного интеллекта.

Области применения технологии CoWoS

Технология CoWoS открывает новые горизонты в мире полупроводников, поддерживая гораздо большее количество транзисторов в корпусе по сравнению со старыми технологиями упаковки, такими как System-in-Chip (SiP). Это делает CoWoS особенно привлекательной для приложений, требующих значительного количества параллельных вычислений, обработки больших векторов данных и высокой пропускной способности памяти.

Основные области применения технологии CoWoS включают в себя высокопроизводительные вычисления (HPC), искусственный интеллект (AI) и машинное обучение (ML), сетевые технологии и центры обработки данных, а также графические процессоры (GPU) и гейминг. Эти сферы особенно выигрывают от возможностей CoWoS по интеграции большого количества транзисторов и обеспечению высокой производительности.

Многие ведущие технологические компании уже успешно применяют пакеты CoWoS в своих продуктах. NVIDIA использует эту технологию для своих чипов искусственного интеллекта, в то время как AMD изучает возможность ее применения в собственных AI-чипах. MediaTek сотрудничает с TSMC для использования CoWoS в своих сетевых ASIC. Broadcom применяет CoWoS-L для ASIC, предназначенных для глубокого обучения и сетевых приложений. Global Unichip Corp. (GUC) также работает с TSMC, интегрируя CoWoS в свои чипы для ИИ, HPC и сетевых приложений.

Эти примеры демонстрируют широкий спектр применения технологии CoWoS в различных секторах полупроводниковой индустрии, подчеркивая ее важность для развития современных высокопроизводительных вычислительных систем.

Заключение

Технология CoWoS представляет собой значительный шаг вперед в области упаковки полупроводниковых устройств, обеспечивая более высокий уровень интеграции и позволяя интегральным схемам масштабироваться в соответствии с растущими требованиями к вычислительной мощности. По мере развития технологии, CoWoS продолжает совершенствоваться, предлагая все более высокую производительность, улучшенное энерго- и теплоснабжение, а также увеличенную площадь интерпозеров, что позволяет размещать больше пластин на одной подложке.

Несмотря на существующие проблемы и ограничения, такие как сложность производства, тепловые и электрические проблемы, технология CoWoS демонстрирует огромный потенциал для дальнейшего развития. Производители и исследователи активно работают над преодолением этих вызовов, что открывает новые возможности для применения CoWoS в различных областях высокопроизводительных вычислений и искусственного интеллекта.

В ближайшие годы ожидается, что технология CoWoS будет продолжать стимулировать рост полупроводниковой промышленности, играя ключевую роль в развитии передовых вычислительных систем. Ее способность обеспечивать высокую производительность и эффективность в сочетании с постоянным совершенствованием делает CoWoS одной из наиболее перспективных технологий в области упаковки полупроводников.

По мере того как требования к вычислительной мощности и эффективности продолжают расти, CoWoS будет оставаться в центре внимания индустрии, способствуя созданию более мощных, энергоэффективных и компактных электронных устройств, которые будут определять будущее технологий.