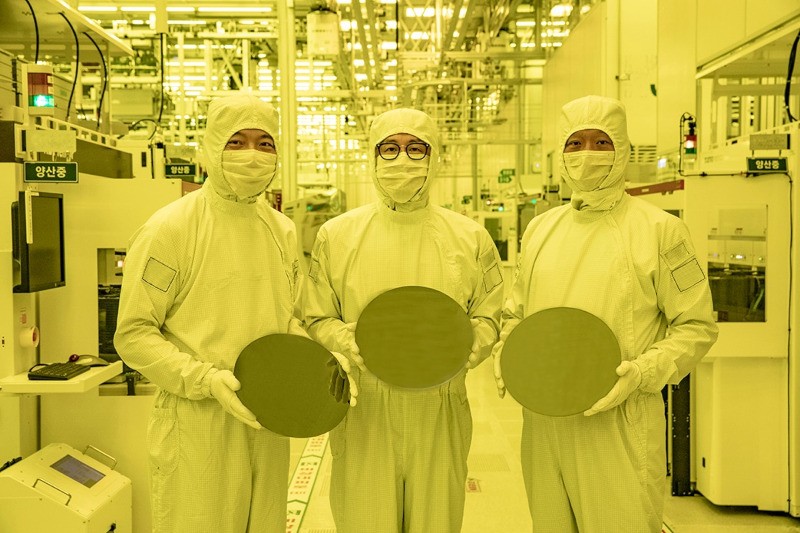

Samsung опережает TSMC в разработке технологии упаковки чипов на уровне панелей

29 июня 2024

29 июня 2024

Samsung Electronics демонстрирует значительный прогресс в разработке технологии упаковки на уровне панелей (Panel Level Packaging, PLP), получив стратегическое преимущество перед своим основным конкурентом TSMC в этом перспективном сегменте полупроводниковой индустрии.

Южнокорейский технологический гигант начал работу над PLP еще в 2015 году, когда TSMC обеспечила себе все заказы Apple на чипы A10 благодаря своей технологии InFO-WLP (Integrated Fan-Out Wafer Level Packaging). В ответ на этот вызов Samsung инициировала сотрудничество с Samsung Electro-Mechanics для разработки технологии Fan-Out Panel Level Packaging (FO-PLP).

Ключевым моментом в развитии PLP-технологии Samsung стало приобретение соответствующего бизнеса у Samsung Electro-Mechanics в 2019 году за 785 миллиардов вон (около 581 миллиона долларов США). Этот стратегический шаг позволил компании сконцентрировать ресурсы и ускорить разработку передовых методов упаковки чипов.

В настоящее время Samsung предлагает широкий спектр передовых услуг по упаковке, включая I-Cube 2.5D, X-Cube 3D IC и 2D FOPKG. Компания также разработала специальные решения для приложений с низким энергопотреблением, таких как мобильные телефоны и носимые устройства.

Бывший глава подразделения полупроводников Samsung Electronics, Кюн Кье-Хюн, подчеркнул важность технологии PLP для отрасли, особенно в контексте растущего спроса на полупроводниковые матрицы для искусственного интеллекта больших размеров (600 х 600 мм или 800 х 800 мм).

В то время как Samsung активно развивает и внедряет PLP-технологию, TSMC только недавно вернулась к ее разработке. Тайваньская компания экспериментирует с прямоугольными подложками размером 515 х 510 мм, что обеспечивает более чем трехкратное увеличение полезной площади по сравнению с традиционной 12-дюймовой пластиной.

Интерес TSMC к PLP объясняется растущим спросом на упаковку передовых чипов для искусственного интеллекта, которые требуют интеграции большего количества транзисторов и памяти. Существующая технология CoWoS от TSMC, способная объединять два набора GPU NVIDIA Blackwell и восемь наборов памяти HBM, может оказаться недостаточной для будущих потребностей рынка.

Таким образом, ранний старт Samsung в разработке PLP-технологии может обеспечить компании значительное преимущество на быстрорастущем рынке передовых методов упаковки чипов, особенно в контексте растущего спроса на решения для искусственного интеллекта.